近日,欧洲设计自动化与测试学术会议(Design, Automation and Test in Europe, DATE)在比利时安特卫普成功举办,电子信息与电气工程学院先进计算机体系结构实验室副教授蒋力和助理教授何哲陟共同指导的博士生汪宗武荣获本届Test and Dependability领域最佳论文奖。

获奖的论文题目为“Self-Terminated Write of Multi-Level Cell ReRAM for Efficient Neuromorphic Computing”,该研究针对现有基于忆阻器存算系统中普遍存在的高阻值不稳定性的问题,提出了多比特精度自适应编程的电路级解决方案,并深度融合现有存算系统,使得ReRAM存算系统的存储密度和算力提升2倍,同时网络权值部署速度和能效分别提升4.7倍和2倍,大幅度降低网络模型部署开销。

研究背景

基于ReRAM忆阻器件的存算一体单元能够将神经网络推理中大规模VMM操作的计算复杂度从O(n2)显著降低到O(1),并大幅降低了大规模数据搬运的时间和能耗开销,有望基于此技术破局传统架构所存在的冯诺依曼瓶颈。但是由于制备工艺、材料研究尚不成熟,ReRAM在实际测试中仍然存在诸多非理想特性,其中影响最大的是ReRAM不同编程次数之间存在的阻值不稳定性和同一次编程中不同器件之间的阻值不稳定性,这严重限制了ReRAM的阻值精度,使得其无法很好地应用于高密度存储和高能效的神经网络存内计算加速。现阶段实现高精度编程的唯一解决方案是广泛应用于传统NVM中的write & verify方案,但该方案每个存储单元编程都需要数十个编程脉冲,映射一个128M权值的VGG-16网络就需要46分钟时间,应用于大规模神经网络权值部署不现实。因此,亟需一种高效高精度的ReRAM的权值映射方案,这也是所有基于忆阻器件的存算系统所必须要解决的关键性问题。

研究成果

继2012年复旦大学Jingang Wu团队在VLSI Symposium上提出Self-Adaptive Write Mode (SAWM)编程方案,实现单比特精度编程以来,不断有来自各个国家的研究团队对该方案进行了改进。但是由于ReRAM阻值变化的随机性以及低延迟特性,导致自适应编程电路需要同时具备高精度和高反馈速度,实现起来具有相当大的挑战性。因此,近几年的工作主要聚焦于低功耗的自适应编程电路,甚至以牺牲控制精度为代价。但是,随着大数据时代对于存储密度的需求不断升高,实现高精度的存储单元编程势在必行,而基于电流叠加原理的存算系统会进一步放大阻值误差带来的影响。该研究从复旦大学提出的SAWM编程电路出发,同时与现有的ReRAM-based存算一体加速系统深度融合。在最大程度复用现有外围电路的基础之上,设计实现了极致紧凑的自适应编程电路,单编程通道只需要额外增加7个晶体管,就可以同时实现对SET和RESET操作的自适应截止,同时紧凑的电路设计还保证了反馈电路的高效性,实现更加精确的阻值控制。

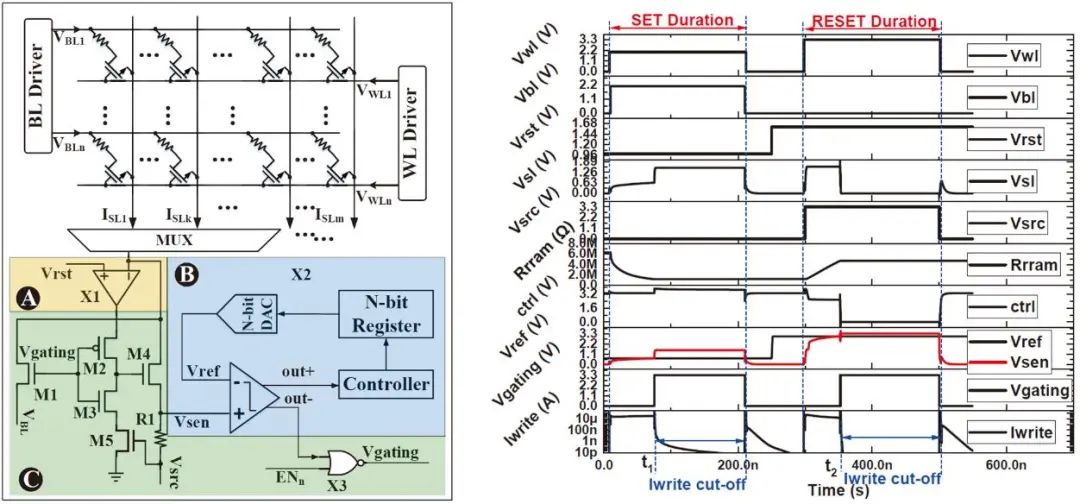

左:自适应电路实现原理图;右:电路仿真波形图

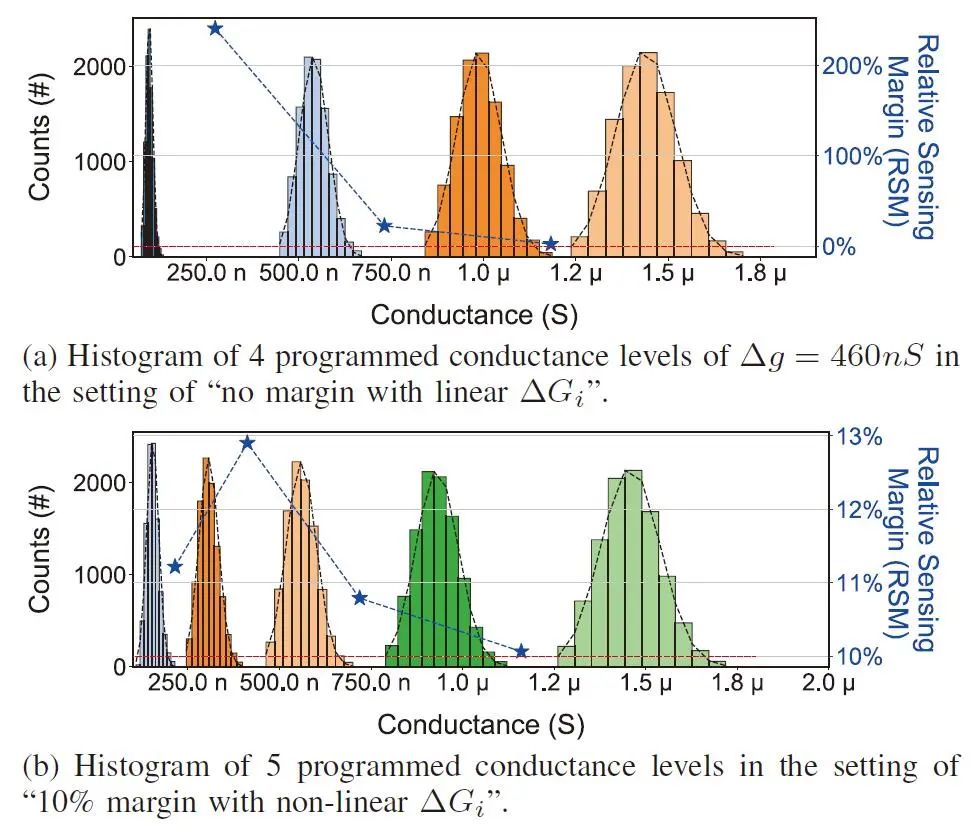

以上示意图分别显示了所设计电路的原理图和Spice仿真结果,可以看出在t1和t2时刻分别实现了SET和RESET编程自适应截止,漏电流低于1nA。Spice仿真中,ReRAM模型和MOSFET模型分别来自于Stanford和商用65 nm PDK。考虑ReRAM和MOSFET的variation,10000次Monte Carlo仿真结果表明:无论是针对于存储系统还是存算系统,该电路都可以实现2比特精度的编程结果,如下图所示:

ReRAM编程阻值分布的Monte Carlo仿真结果

欧洲设计自动化与测试学术会议(Design, Automation and Test in Europe,DATE)

DATE是固定在欧洲每年举行的电子设计自动化的主题会议,创办三十年来,DATE已经成为全球电子设计与测试领域的著名学者、企业界专家的交流盛会。会议涉及电子和(嵌入式)系统工程技术研究的各个方面,涵盖了从集成电路到大规模分布式系统的电子产品设计自动化的设计、测试和工具。会议范围还包括为电信、无线通信、多媒体、医疗保健和汽车系统等具有挑战性的应用领域制定设计要求和新架构。

论文链接:https://github.com/ZongwuWang/DATE_2022

文稿丨汪宗武