Jingwen Leng, Yazhou Zu, and Vijay Janapa Reddi

In Proc. of International Symposium on High Performance Computer Architecture (HPCA), 2015.

ABSTRACT

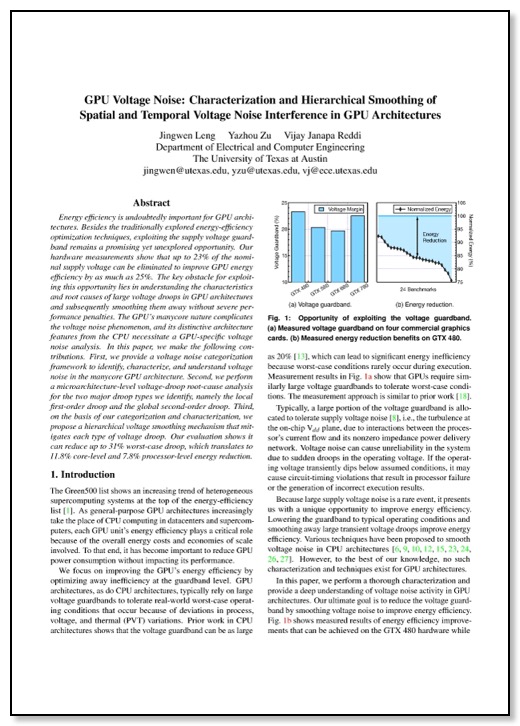

Energy efficiency is becoming important for GPU architectures. Besides the traditionally explored energy-efficiency optimization techniques, exploiting the supply voltage guardband remains a promising yet unexplored opportunity. Hardware measurements show that up to 23% of the nominal supply voltage can be eliminated to improve GPU energy efficiency by as much as 25%. However, the key obstacle for exploiting this opportunity lies in understanding the characteristics and root causes of large voltage droops in GPU architectures and subsequently smoothing them away without introducing timing violations or severe performance penalties. The GPU's many-core nature complicates the voltage noise phenomenon, and its distinctive architecture features from the CPU necessitate a GPU-specific voltage noise analysis. In this paper, we make the following contributions. First, we provide a voltage noise categorization framework to identify, characterize, and understand voltage noise in the many-core GPU architecture. Second, we perform a microarchitecture-level voltage-droop root-cause analysis for the two major droop types we identify, namely the local first-order droop and the global second-order droop. Third, on the basis of our categorization and characterization, we propose a hierarchical voltage smoothing mechanism that mitigates each type of voltage droop. Our evaluation shows up to 31% worst-case droop and 99% voltage emergencies (voltage droops larger than 8%) can be reduced, which translates to 11.8% core-level and 7.8% processor-level energy reduction.